# Message scheduling to reduce AFDX jitter in a mixed NoC/AFDX architecture

#### Jérôme Ermont, Sandrine Mouysset, Jean-Luc Scharbarg and Christian Fraboul

Université de Toulouse - IRIT - INPT/ENSEEIHT

October 12, 2018

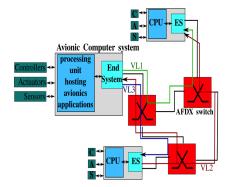

## Context: Avionics architecture of modern planes

- Avionics computers:

- Mono-core processors: execute avionics functions following IMA (Integrated Modular Avionics)

- End Systems: interface between CPU and AFDX

- AFDX network:

- Interconnection of several avionics computers

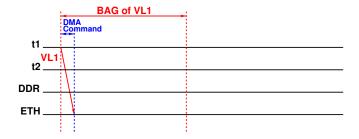

- VL: unidirectionnal flow between one source ES to one or more destination ES

- BAG: minimum interval time between 2 frames of a VL

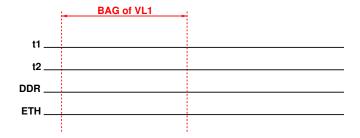

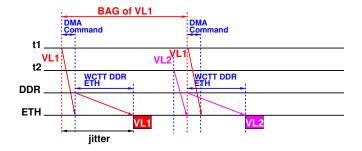

# Transmission of VLs by an ES

- VLs from different partitions share the same ES

- Scheduler between VLs into the ES

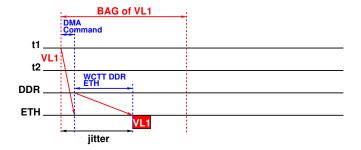

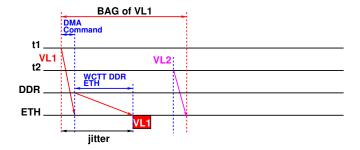

- Introduces a jitter: delay between the beginning of the BAG and the effective transmission of the frame

- AFDX constraint: jitter < 500  $\mu$ s

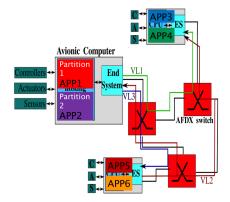

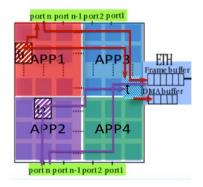

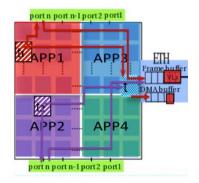

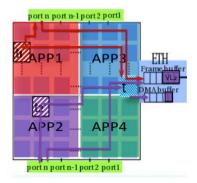

## Envisioned avionics architecture

- To replace mono-core processing unit by many-cores

- Different applications can be executed in parallel

- 2 different communications:

- Intra-NoC communication

- Inter-NoC communication

- The jitter depends on the WCTT of flows from other applications

- WCTT depends on the blocking mechanism of the NoC

- The jitter depends on the WCTT of flows from other applications

- WCTT depends on the blocking mechanism of the NoC

#### Problem

How to reduce the jitter induced by the transmission on the NoC ?

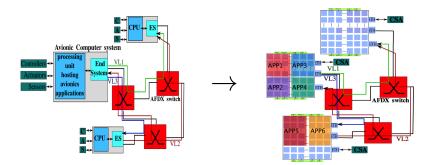

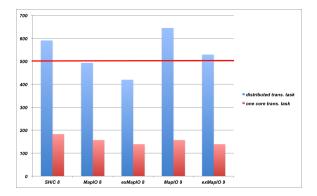

# A first solution: minimizing the contention for other applications

• A new application mapping: Extended Map<sub>IO</sub> [1]

• Minimizing contentions reduces the maximum jitter

• But not for all configurations

[1] Towards a mixed NoC/AFDX architecture for avionics applications, Laure Abdallah and al., WFCS 2017

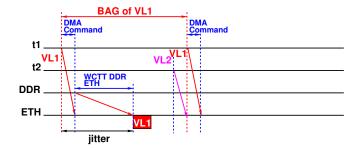

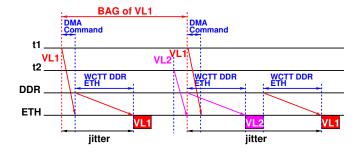

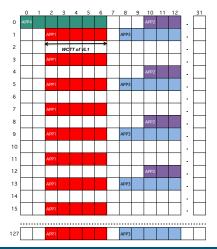

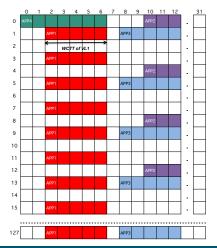

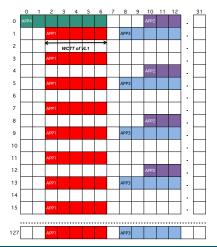

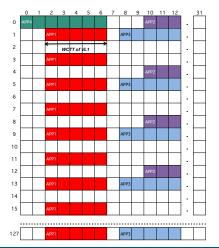

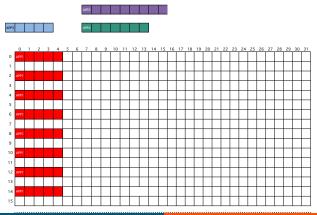

- One node dedicated to schedule the VLs on the ES

- Use of a TDMA table

- One node dedicated to schedule the VLs on the ES

- Use of a TDMA table

- One node dedicated to schedule the VLs on the ES

- Use of a TDMA table

- One node dedicated to schedule the VLs on the ES

- Use of a TDMA table

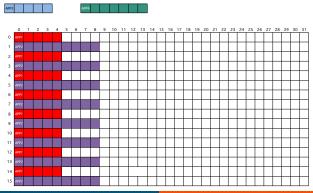

- Bag of VL4 (from App4): 128 ms

- VL4 is ready when line 6 of the table is executed

- One node dedicated to schedule the VLs on the ES

- Use of a TDMA table

- Bag of VL4 (from App4): 128 ms

- VL4 is ready when line 6 of the table is executed

- VL4 will wait line 0

- One node dedicated to schedule the VLs on the ES

- Use of a TDMA table

- Bag of VL4 (from App4): 128 ms

- VL4 is ready when line 6 of the table is executed

- VL4 will wait line 0

How to reduce this waiting delay ?

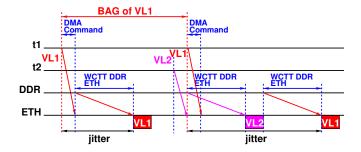

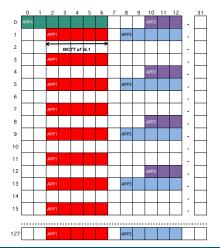

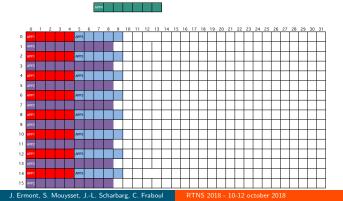

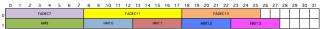

#### Our solution

To give more slots for the VLs  $\rightarrow$  Oversampling of slots

- One node dedicated to schedule the VLs on the ES

- Use of a TDMA table

- Bag of VL4 (from App4): 128 ms

- VL4 is ready when line 6 of the table is executed

- VL4 will wait line 0

How to reduce this waiting delay ?

#### Our solution

To give more slots for the VLs  $\rightarrow$  Oversampling of slots

#### Constraint

- VLs with BAG = 1ms allocated to all lines

- Allocation by considering the minimum BAG value (> 1ms)

| APP1 |   |   |   |   |   |   |   | APP2 |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|------|---|---|---|---|---|---|---|------|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| АРРЗ |   |   |   |   |   |   |   | APP4 |   |   |    |    |    |    | l  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|      | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7    | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

| 0    |   |   |   |   |   |   |   |      |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 1    |   |   |   |   |   |   |   |      |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 2    |   |   |   |   |   |   |   |      |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 3    |   |   |   |   |   |   |   |      |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 4    |   |   |   |   |   |   |   |      |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 5    |   |   |   |   |   |   |   |      |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 6    |   |   |   |   |   |   |   |      |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 7    |   |   |   |   |   |   |   |      |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 8    |   |   |   |   |   |   |   |      |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 9    |   |   |   |   |   |   |   |      |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 10   |   |   |   |   |   |   |   |      |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 11   |   |   |   |   |   |   |   |      |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 12   |   |   |   |   |   |   |   |      |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 13   |   |   |   |   |   |   |   |      |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 14   |   |   |   |   |   |   |   |      |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 15   |   |   |   |   |   |   |   |      |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|      |   |   |   |   |   |   |   |      |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

#### Constraint

- VLs with BAG = 1ms allocated to all lines

- Allocation by considering the minimum BAG value (> 1ms)

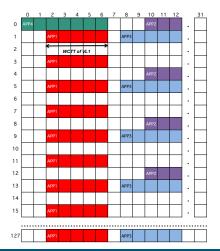

#### Constraint

- VLs with BAG = 1ms allocated to all lines

- Allocation by considering the minimum BAG value (> 1ms)

#### Constraint

- VLs with BAG = 1ms allocated to all lines

- Allocation by considering the minimum BAG value (> 1ms)

#### Constraint

- VLs with BAG = 1ms allocated to all lines

- Allocation by considering the minimum BAG value (> 1ms)

# Formulation by a Bin Packing Problem

#### Objective

To allocate VL transmissions into a minimum number of lines

• Number of lines in which VLs are allocated

$$N = \min_{j=1...m, BAG_j \neq 1} BAG_j$$

Objective function

$$\begin{array}{ll} \min & \sum_{i=1}^{N} y_i \\ s.t & \sum_{j=1}^{m} \omega_j x_{ij} & \leq C \ y_i, \forall i = 1, ..., N \\ & \sum_{i=1}^{N} x_{ij} & = 1, \forall j = 1, ..., m \\ & y_i \in \{0, 1\} & , \forall i = 1, ..., N \\ & x_{ij} \in \{0, 1\} & , \forall i = 1, ..., N, \forall j = 1, ..., m. \end{array}$$

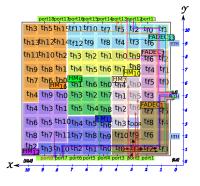

## Evaluation case study

- A 10×10 Tilera-like NoC

- 2 types of applications:

FADEC: engine control

- critical application

- little amount of exchanged data: 1500 bytes

- full transmission between task

#### HM: HouseKeeping

- non-critical application

- lots of data exchanged: > 130 Koctets

- data are stored in the memory

- 9 (critical or non-critical) considered applications: FADEC<sub>7</sub> (4), FADEC<sub>11</sub> (8), FADEC<sub>13</sub> (16), HM<sub>7</sub> (4), HM<sub>9</sub> (2), HM<sub>10</sub> (16), HM<sub>11</sub> (32), HM<sub>12</sub> (16), HM<sub>16</sub> (32)

- 2 system configurations:

- 8 applications: HM<sub>7</sub> is removed

- 9 applications

- 3 mapping strategies:

- SHiC [1]: mapping by considering the core-to-core communications

- Map<sub>IO</sub> [2]: mapping by considering core-to-IO communications

- exMap<sub>IO</sub> [3]: mapping by considering both core-to-IO and IO-to-core communications

[1] Smart hill climbing for agile dynamic mapping in many-core systems, Mohammad Fattah and al

[2] Reducing the contention experienced by real-time core-to-I/O flows over a Tilera-like Network on Chip, Laure Abdallah and al., ECRTS 2016

[3] Towards a mixed NoC/AFDX architecture for avionics applications, Laure Abdallah and al., WFCS 2017

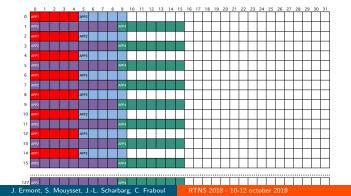

## VLs transmissions packed into the table

#### SHiC

|   | 0 | 1 | 2 | 3   | 4   | 5 | 6 | 7 | 8 | 9 | 10   | 11 | 12  | 13   | 14 | 15    | 16 | 17 | 18 | 19 | 20   | 21  | 22   | 23 | 24 | 25   | 26 | 27 | 28 | 29 | 30 | 31 |

|---|---|---|---|-----|-----|---|---|---|---|---|------|----|-----|------|----|-------|----|----|----|----|------|-----|------|----|----|------|----|----|----|----|----|----|

| 0 |   |   |   | FAD | EC7 |   |   |   |   |   |      |    | FAD | EC11 |    |       |    |    |    |    |      | FAD | EC13 |    |    |      |    |    |    |    |    |    |

| 1 |   |   |   | н   | M9  |   |   |   |   |   | нм10 |    |     |      |    | HM1 1 |    |    |    |    | HM12 |     |      |    |    | HM13 | 3  |    |    |    |    |    |

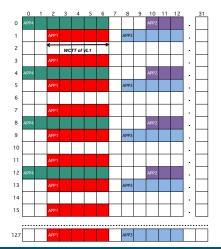

#### • MapIO with 8 applications

|   | 0 | 1 | 2   | 3   | 4 | 5 | 6 | 7  | 8  | 9   | 10   | 11 | 12 | 13   | 14 | 15 | 16  | 17  | 18   | 19 | 20 | 21 | 22 | 23 | 24 | 25   | 26 | 27 | 28 | 29 | 30 | 31 |

|---|---|---|-----|-----|---|---|---|----|----|-----|------|----|----|------|----|----|-----|-----|------|----|----|----|----|----|----|------|----|----|----|----|----|----|

| 0 |   |   | FAD | EC7 |   |   |   |    |    | FAD | EC11 |    |    |      |    |    | FAD | C13 |      |    |    |    |    |    |    |      |    |    |    |    |    |    |

| 1 |   |   | HM9 |     |   |   |   | HN | 10 |     |      |    |    | HM11 |    |    |     |     | HM12 |    |    |    |    |    |    | HM13 |    |    |    |    |    |    |

#### • Ex\_Map<sub>IO</sub> with 8 applications

|   | 0 | 1 | 2   | 3   | 4 | 5 | 6 | 7  | 8  | 9   | 10 | 11 | 12 | 13   | 14 | 15  | 16  | 17 | 18   | 19 | 20 | 21 | 22 | 23 | 24 | 25   | 26 | 27 | 28 | 29 | 30 | 31 |

|---|---|---|-----|-----|---|---|---|----|----|-----|----|----|----|------|----|-----|-----|----|------|----|----|----|----|----|----|------|----|----|----|----|----|----|

| 0 |   |   | FAD | EC7 |   |   |   |    | F/ | DEC | 1  |    |    |      |    | FAD | C13 |    |      |    |    |    |    |    |    |      |    |    |    |    |    |    |

| 1 |   |   | HM9 |     |   |   |   | HM | 10 |     |    |    |    | HM11 |    |     |     |    | HM12 |    |    |    |    |    |    | HM13 | 3  |    |    |    |    |    |

#### Map<sub>IO</sub> with 9 applications

|   | 0 | 1 | 2   | 3   | 4    | 5 | 6 | 7 | 8   | 9   | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26   | 27  | 28 | 29 | 30 | 31 |

|---|---|---|-----|-----|------|---|---|---|-----|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|------|-----|----|----|----|----|

| 0 |   |   | FAD | EC7 |      |   |   |   | FAD | C13 |    |    |    |    | н  | 49 |    |    |    |    | HM | 10 |    |    |    |    | HM   | 111 |    |    |    |    |

| 1 |   |   |     | FAD | EC11 |   |   |   |     |     |    | H  | 47 |    |    |    |    |    | HM | 12 |    |    |    |    |    |    | HM13 | 3   |    |    |    |    |

#### • Ex\_Map<sub>IO</sub> with 9 applications

|   | 0 | 1 | 2   | 3    | 4  | 5 | 6 | 7 | 8   | 9    | 10  | 11 | 12 | 13 | 14  | 15 | 16 | 17 | 18 | 19 | 20  | 21 | 22 | 23 | 24  | 25 | 26  | 27 | 28 | 29 | 30 | 31 |

|---|---|---|-----|------|----|---|---|---|-----|------|-----|----|----|----|-----|----|----|----|----|----|-----|----|----|----|-----|----|-----|----|----|----|----|----|

| 0 |   |   | FAD | EC7  |    |   |   |   | FAD | EC13 |     |    |    |    | HM9 |    |    |    |    | HM | (10 |    |    |    |     | HM | 411 |    |    |    |    |    |

| 1 |   |   | E   | ADEC | 11 |   |   |   |     |      | HM7 |    |    |    |     |    | HM | 12 |    |    |     |    |    |    | HM1 | 3  |     |    |    |    |    |    |

### Results

- TDMA table guarantees the transmission every BAG

- Jitter constraint is respected when using a dedicated node

# Conclusion

- To replace mono-core processors by NoC based many-cores architecture

- Sharing the same output port could lead to an execution for which the jitter constraint is exceeded

- Mapping strategy Extended Map<sub>IO</sub> minimizes the jitter by reducing the contention

- But jitter constraint can be exceeded

- Our proposition: one dedicated node schedules the outgoing flows using a TDMA table

- The jitter only depends on the contentions for the outgoing flow

- The jitter is then significantly reduced

- Construction of a scheduling table

- Guarantee of the BAG constraint

- Over allocation of slots in order to reduce waiting delays

#### SHiC mapping example

- What happens if HM<sub>13</sub> needs 10 slots ?

- Different possible solutions

- Reduce more the contentions on outgoing flows

- Relax the constraint of the minimum number of lines for larger BAG value  $\rightarrow$  Variable capacity size bin packing or cutting stock problem

- Global transmission delay from one manycore to another via AFDX

- Implementation of the solution in a real manycore system such as Tilera or Kalray